存算一体是模拟系统和存储系统的设计,比标准模拟IP和存储器IP更庞大更复杂,依赖于多次流片而积累的经验,走向成熟预计需要5-10年 。

编者按:本文来自微信公众号松禾资本(ID:greenpinevc),作者:松禾资本成长基金投资总监 管国根,创业邦经授权发布

存算一体最近特别火,今年仅国内就出现了多家存算一体芯片公司,包括阿里达摩院刚发布的基于DRAM的存算一体芯片技术,旨在把传统以计算为中心的架构转变为以数据为中心的架构,其直接利用存储器进行数据处理,从而把数据存储与计算融合在同一个芯片当中,可以消除冯诺依曼计算架构瓶颈,特别适用于AI大数据量大规模并行的应用场景。下面我们就来详细解析一下存算一体这个行业。

1969年,斯坦福研究所的Kautz等人提出了存算一体计算机的概念。后续许多研究工作在芯片电路、计算架构、操作系统、系统应用等层面展开,但受限于芯片设计、制造成本、应用场景问题,早期存算一体仅仅停留在理论研究阶段,并未得到实际应用。

近年来,非易失性存储器技术,如闪存(FLASH)、忆阻器(阻变存储器RRAM)、相变存储器(PCM)和与自旋磁存储器(MRAM)等,为存算一体提供新的解决路线。2010年,惠普实验室的Williams教授团队提出并验证利用忆阻器实现简单布尔逻辑功能(联合、相交、相减等)。2016年,美国加州大学圣塔芭芭拉分校(UCSB)的谢源教授团队提出利用RRAM构建基于存算一体架构的深度学习神经网络(PRIME)。测试表明,相较于传统冯诺伊曼架构的传统方案,PRIME可以实现功耗降低约20倍、速度提高约50倍。同年,UCSB发布第一个基于Nor Flash的存算一体芯片,引起产业界广泛关注,国内外多家初创企业据此展开研发。随着物联网、人工智能等大数据应用的兴起,技术得到国内外学术界与产业界的广泛研究与应用。在2017年微处理器顶级年会(Micro 2017)上,包括英伟达、英特尔、微软、三星、苏黎世联邦理工学院与加州大学圣塔芭芭拉分校等都推出了他们的存算一体系统原型。

惠普实验室忆阻器团队,从左到右分别是Dmitri Strukov, Stan Williams, Duncan Stewart, Greg Snider

目前,存算一体的商业驱动力主要源于AI算力的需求、并行计算在深度学习的广泛应用、深度学习市场潜力对人工智能发展的推动和摩尔定律的成本攀升。

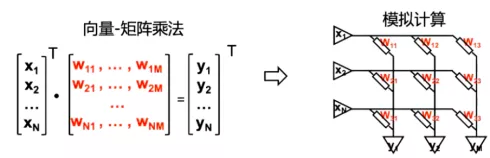

基于神经网络的人工智能的兴起,尤其是移动端和嵌入式设备的人工智能场景,让高能效比的存内计算获得了广泛关注。一个典型运算中包括两个运算“输入”和一个运算“操作”。在众多科学计算应用中两者都是实时产生的,存内计算意义不大。而在神经网络运算中,其运算权重固定,仅“输入”是实时产生,因此可以将权重存在内存,等外部“输入”进入后再进行高能效的存内计算需求产生。同时,神经网络推理对计算精度的误差拥有较高的容忍度,存内计算的模拟计算中引入的误差往往可以被神经网络所接受。

此外,新型存储器的出现也带动了存算一体技术的发展,为存算一体技术升级方向提供可能。其中,阻变忆阻器ReRAM使用电阻调制来实现数据存储,读出电流信号而非传统的电荷信号。由于电流做累加运算更加方便,无需额外电路,ReRAM在神经网络计算中具有特别的优势。因此,新型存储器与存算一体技术的结合,有望推动下一阶段的人工智能发展。

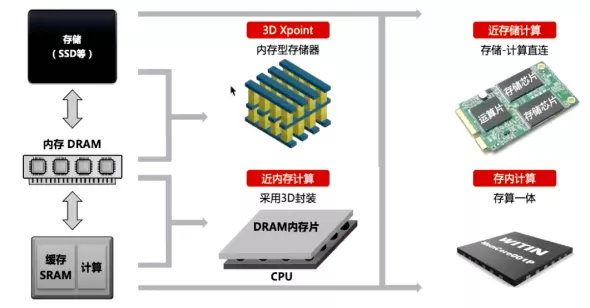

为了打破冯诺依曼计算架构瓶颈,降低“存储-内存-处理单元”过程数据搬移带来的开销,近十年有几种方式。其中比较直接的方法是近内存计算,减少内存和处理单元之间的路径,如通过3D封装技术实现3D堆叠,将多层DRAM堆叠而成的新型内存,能提供更大的内存容量和内存带宽。此外,Intel和Micron合作开发的基于PCRAM存储介质的3D Xpoint属于内存型存储器,旨在缩短存储与内存之间的路径。但由于有限性能、高昂成本及配套生态限制,2021年Micron宣布停止3D Xpoint开发。上述方案并没有改变数据存储与数据处理分离的问题,只能在一定程度上缓解,但是并不能从根本上解决冯诺依曼计算架构瓶颈。

存内计算,即存算一体技术直接利用存储器进行数据处理,从而把数据存储与计算融合在同一个芯片当中,可以彻底消除冯诺依曼计算架构瓶颈,特别适用于深度学习神经网络这种大数据量大规模并行的应用场景。广义上,近存储计算也被归纳为存算一体的技术路径之一。将简单运算放在存储旁边的小计算单元完成,存储与计算直连,不占用CPU的计算空间,减少数据搬运损耗。

新型内存计算四种方式

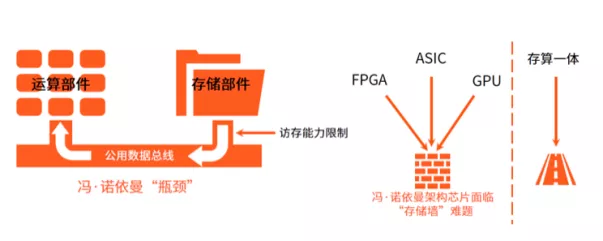

冯诺伊曼架构是目前计算机以及处理器芯片的主流传统架构。在冯诺伊曼架构中,计算单元与内存是两个分离的单元:计算单元根据指令从内存中读取数据,在计算单元中完成计算和处理,完成后再将数据存回内存。在这个过程中,存储器与处理器之间数据交换通路窄以及由此引发的高能耗形成两大难题,在存储与运算之间筑起一道“存储墙”。能耗方面,大部分能耗在数据搬运过程中产生,数据搬运功耗是计算功耗的1000倍。而数据搬运速度方面,AI运算需1PB/s,但SRAM 10-100TB/s、DRAM 40GB-1TB/s 都远达不到要求。

存算一体技术将计算机中的运算从中央处理器转入内存中进行,使用储存器件单元直接完成数据处理,无需数据读写和搬运,可大幅降低数据交换时间以及计算过程中的数据存取的能耗,消除冯诺依曼计算架构瓶颈。在存算一体中,单个储存单元可以完成8-bit乘加法运算,而在传统架构中则需要2500晶体管。同时,整个矩阵的运算可并行完成,效率提升50~100倍。

冯诺伊曼“存储墙”图解

1.存内计算

将带权重加乘计算的权重部分存在内存单元中,在内存的核心电路上做修改,从而在读取的同时进行数据输入和计算处理,在内存中完成卷积运算。由于卷积运算是深度学习算法中的核心组成部分,因此存内计算非常适合人工智能的深度神经网络应用。

基于RRAM/FLASH/PCM的矩阵运算权重基本原理

2.感存算

集传感、储存和运算为一体构建感存算一体架构,解决冯诺依曼架构的数据搬运的功耗瓶颈,同时与传感结合提高整体效率。国内XX公司的智能视觉传感器是感存算的一种运用,在传感器自身包含的“模拟域”上运算,来实现超高、零延时和超低功耗的智能视觉处理能力。基于SRAM模数混合的视觉应用存内计算神经拟态芯片仅在检测到有意义的时间才会进行处理,大幅降低能耗。

3.类脑计算

通过将电子元件编程为离散阻值状态并将不同权重的电子元件相互卷积以建立一个类似突触和神经元的系统,即神经拟态计算,又被称为类脑计算。其设计极其复杂,距离应用还有很长一段距离(清华大学类脑计算团队打造的异构融合类脑计算芯片)。

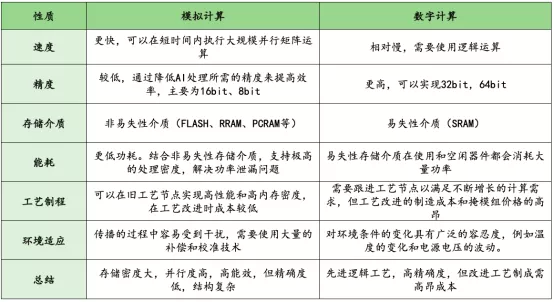

存算一体的计算方式分为数字计算和多比特模拟计算。模拟计算存算一体数字计算主要以SRAM作为存储器件,采用先进逻辑工艺。而模拟计算通常使用FLASH、RRAM、PCRAM等非易失性介质作为存储器件,存储密度大,并行度高。数字计算具有高精度、高环境容忍度的优点,但是模拟计算在速度、能耗、工艺节点方面有优势。

存算一体计算方式

目前可用于存算一体的成熟存储器有NorFLASH、SRAM、DRAM。FLASH属于非易失性存储介质,具有低成本、高可靠性的优势,但在工艺制成有瓶颈。SRAM在速度方面具有优势,但是其容量密度小,价格昂贵,在大阵列运算的同时难保证运算精度。DRAM成本低,容量大,但是速度慢,且需要电力不断刷新。

新型存储器有PCRAM、MRAM、ReRAM和FeRAM等,其中阻变忆阻器ReRAM在神经网络计算中具有特别的优势,是目前存算一体下一代存储介质的主流研究方向。ReRAM使用电阻调制来实现数据存储,读出电流信号而非传统的电荷信号,电流做累加运算更加方便,无需额外电路。但目前ReRAM距离工艺成熟还需要1-2年,材料不稳定,但ReRAM具有高速度、长寿命、结构简单的优点,是今年发展最快的新型存储器。此外,Intel和Micron还提出了PCRAM的内存计算应用,将其作为3D Xpoint内存型存储器,提升SSD与内存之间的效率。纯3D Xpoint芯片的傲腾已量产,成本高昂,且需要配套的高规格软硬件。而其在容量性价比、读写能力并没有与成本相呼应的提升,客户接受度很低。2021年美光宣布退出3D Xpoint项目,Intel表示将纯3D Xpoint产品线退役,该技术将结合QLC作为混合形态的固态盘,混合形态的性能表现远不及纯3D Xpoint。

“先进存储技术升级”在“十四五纲要”中被列为重点

国家“十四五”规划纲要中,在加强原创性引领性科技攻关方面,“先进存储技术升级”被列入“科技前沿领域攻关”重点领域;在加快推动数字产业化方面,《纲要》提到,培育壮大人工智能、大数据、区块链、云计算、网络安全等新兴数字产业,提升通信设备、核心电子元器件、关键软件等产业水平。

“临港专项规划”针对EDA、关键IP、高端芯片等方面作出重点支持

2021年3月,上海临港新片区发布集成电路产业专项规划(2021-2025),提到要“积极引进国内外EDA工具/IP企业”,“在阻变存储器(ReRAM)等新兴领域实现增量发展”。

长三角面向物联网领域推进“感存算一体化”合作

2020年6月6日,长三角物联网“感存算一体化”合作落地。11月18日,长三角“感存算一体化”联盟正式成立,长三角“科技+产业”合作项目同时签约。

长三角面向物联网领域“感存算一体化”超级中试中心战略合作框架协议,由上海嘉定、江苏无锡、浙江杭州、安徽合肥人民政府,以及中电海康集团有限公司共同签约。拟加强沪苏浙皖分工合作,按照中试设备互补共享、产业布局错位衔接、市场应用统一完整的原则,共建跨区域超级中试中心,实现四个千亿的产业集群,打造全球物联网高地。

1. 智能可穿戴设备市场

2020年中国智能可穿戴设备市场总规模632.2亿元,预计2025年规模达1465.6亿元,复合增长率约17.9%。智能可穿戴分为商业消费级设备和专业医疗级设备。其中,商业消费级设备为主流,预计2025年市场规模达1105.6亿元。

数据来源:头豹研究院

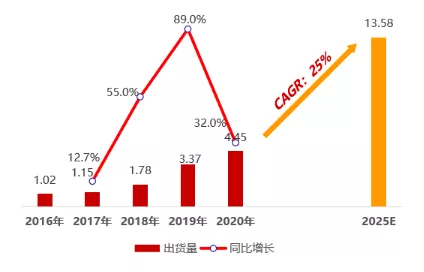

2020年全球智能可穿戴设备出货量达4.45亿台,预计2025年出货量达13.58亿台,年复合增长率达25%。2020年中国出货量为1.07亿台,预计2025年出货量达2.66亿台,年复合增长率20%。

2016-2025年全球智能可穿戴设备出货量(单位:亿台)

2016-2025年中国智能可穿戴设备出货量(单位:亿台)

数据来源:IDC、健康界研究院分析

智能可穿戴行业具有高同质化特点,耳机、手表、手环三者市场全球合计占有率高达99%,中国占有率也高达95%。预计全球智能耳机、手表出货量保持年复合增长率(CAGR)14%,总体全球智能穿戴行业预计CAGR达12.4%。

2020-2024年全球智能穿戴设备出货量及市场份额预

2019年中国智能穿戴市场各产品占比

数据来源:IDC、巨量数算

2. 智能家居

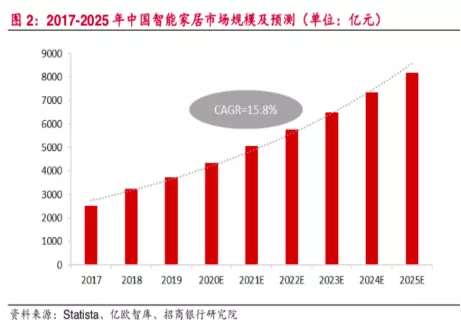

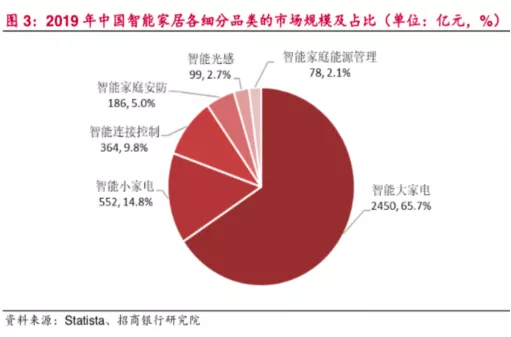

据预测,2025 年中国智能家居市场规模将突破 8000 亿元,年复合增长率高达15.8%。细分市场来看,品类之间市场规模及占比差别较大。规模最大的智能大家电市场规模达到了 2450 亿元,占比达到 65.7%, 而智能光感的市场空间仅为 99 亿元,占比 2.7%。

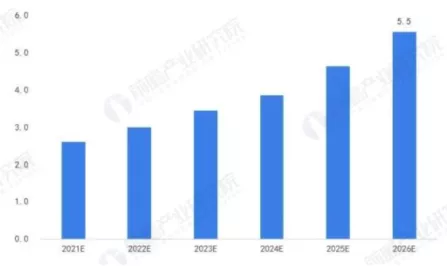

2021年,中国智能家居设备全年出货量将接近2.6亿台,同比增长26.7%。据预测,2026年中国智能家居出货量将达5.5亿台。

2021-2026年中国智能家居设备出货量预测

数据来源:前瞻产业研究院

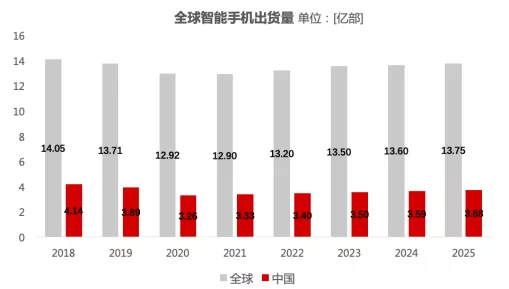

3. 智能手机

2016-2020年,全球及中国智能手机市场在到达2016年的出货量顶峰后均逐渐下滑,中国智能手机出货量降速明显。预计2021-2025年全球及中国智能手机出货量将有所回升并趋于稳定,预计全球年复合增长率1.2%,中国2.5%。

数据来源:头豹研究院

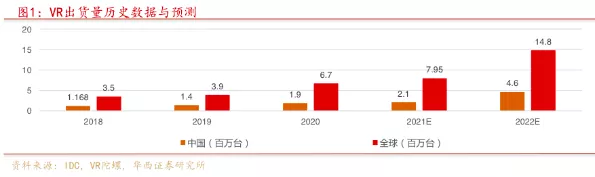

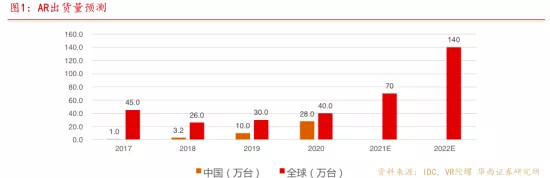

4. VR/AR

2020年全球VR出货量670万台,同比增长72%。21年预计全球出货量达到约800万台,22年预计1480万台。国内方面,2020年出货量为190万台,预计2021年出货210万台,2022年4.6万台,呈向上增长态势。未来VR应用场景将主打游戏功能。

2020年全球AR出货量40万台,同比增长33%。预计2021年全球出货70万台,22年出货150万台。目前AR行业尚未成熟,出货量少,上游处于核心零部件和技术的攻关阶段,下游生态不成熟,产品定位尚未清晰。

5.智能安防

据估算,2020年我国智能安防市场规模约为576亿元。未来安防行业将向智能化深度发展,智能安防市场规模也将持续增长,预计到2026年,市场规模有望突破2500亿。

2013-2020年中国智能安防行业市场规模(单位:亿元)

2021-2026年中国智能安防行业市场规模(单位:亿元)

6.低速无人车市场

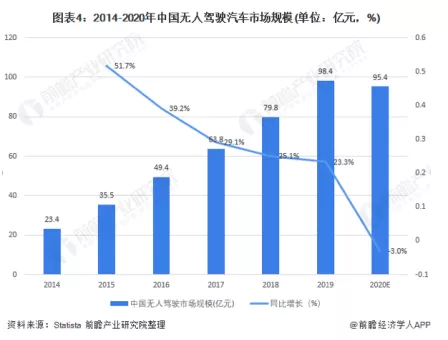

根据Statista数据显示,2015年到2019年我国无人驾驶汽车行业市场规模扩张迅速,2019年我国无人驾驶汽车市场规模达到98.4亿元,2020年受疫情影响市场规模将有所下滑至 95.4亿元。在Research And Markets的预测下,2021年全球无人驾驶汽车的市场规模将达273亿美元,2026年全球无人驾驶汽车市场规模将达到594亿美元,年复合增长率为16.84%。

2014-2020年中国无人驾驶汽车市场规模(单位:亿元)

2021-2026年全球无人驾驶汽车市场规模预测(单位:亿美元)

7.智能驾驶

近年来我国智能驾驶行业发展迅速,2016至2020年,中国智能驾驶市场规模从490亿元提升至1702亿元,市场前景广阔。据中金测算,2025年中国/全球智能驾驶人工智能SoC芯片市场规模有望达到49亿/147亿美元。

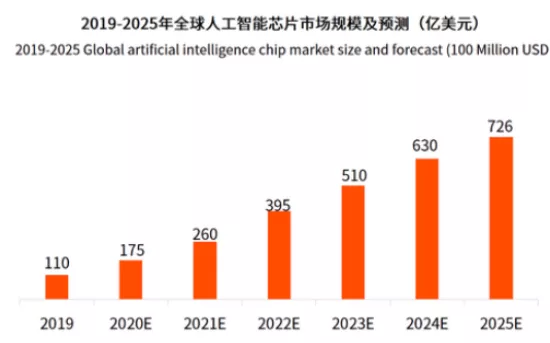

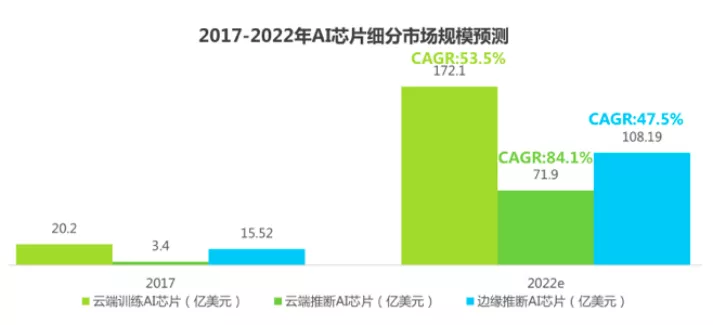

2019年全球人工智能芯片市场规模达110亿美元,预计2025年市场规模将达到726亿美元。人工智能芯片可细分为云端训练、云端推理和边缘端推理。根据中金预测,2022年云端训练AI芯片全球市场规模将达172亿美元,云端推理AI芯片全球规模超70亿美元,边缘端推断AI芯片超100亿美元,均保持高水平年复合增长率。

数据来源:艾漫咨询

数据来源:中金公司研究部

1、更高精度

工艺优化:过去的工艺优化主要是根据存储器工艺,并没有针对存算一体的应用专门做优化。若能针对性优化,对存算一体的精度、模拟计算电流、线性度、持久性等能有大幅度提高。但工艺优化的周期较长,投入较大,需好几年才能完成一代工艺优化。随着存算一体的迅速发展,针对性的工艺优化成为可能。

数模混合计算:数模混合计算架构能提高精度、纠错、数据压缩能力,但通用性较低。

2、更高算力

先进封装(如Chiplet、2.5D封装):Chiplet与存算一体的结合,平面上可以集成多个存储和逻辑芯片,且存储、模拟、逻辑可以采用不同的工艺。目前Chiplet技术正在发展,未来两三年需面临建立标准测试方法、高封装成本、无标准化接口的问题。

3D堆叠方案:可以集成多层存储、逻辑和模拟,且存储、模拟、逻辑可以采用不同的工艺。目前在存储器内使用得较多,若针对非标准的场景使用3D堆叠方案,可能会有较高的研发周期和成本。

3、更高能效

新型存储器介质、先进工艺尺寸、模拟计算技术进步都能对能效有进一步提升。

1、计算精度有限。

现有浮栅存储器件并不适合用于计算,且片内存储本质上使用模拟计算,计算精度会受到模拟计算低信噪比的影响,通常精度上限在8 bit左右,而且只能做定点数计算,难以实现精准的浮点数计算。因此并不适用于需要高计算精度的人工智能训练场景,仅适用于嵌入式人工智能等对于能效比有高要求而对于精确度有一定容忍的场景。

2、应用落地场景边界条件限制较多。

存内计算仅适合原本就对存储需求较大的场景,而对于本身存储需求并不高的场景,为了引入内存计算而加上一块大内存反倒会增加成本适得其反。尤其是随着内存容量的增加,内存成本往往呈指数级增长,且内存容量上限有限,性价比不理想导致内存计算无法惠及更多用户、更多场景。目前来看,在人工智能本身仍在探寻应用场景的前提下,存算一体化的落地问题,仍需要紧密结合具体应用场景具体分析。

3、芯片开发生态亟待打造。

存算一体芯片产业化尚处于起步阶段,目前仍面临产业链上游支撑不足,下游应用不匹配等诸多困局。例如,在芯片设计阶段,由于存算一体芯片区别于常规的芯片设计方案,所以目前市面上没有成熟的专用EDA工具辅助设计和仿真验证;芯片流片之后,也没有成熟的工具协助测试;在芯片落地应用阶段,暂时没有专用的软件与之匹配。因此,亟须围绕存算一体打造生态。

存算一体市场处于早期百家争鸣,产业生态构建中。自2016年UCSB发布存算一体AI芯片第一个样片以来,多家国内外初创企业陆续开展相关研发,如美国Mythic、Syntiant、中国xx半导体等,并得到包括Intel、ARM、Bosch、Amazon、Microsoft、Softbank、中芯国际等国内外主流半导体企业与资本的产业投资。

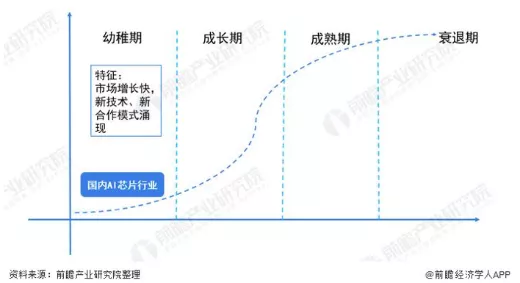

我国人工智能芯片行业处于快速增长的幼稚期。国内人工智能芯片行业的整体市场正处于快速增长阶段,传统芯片的应用场景逐渐被人工智能专用芯片所取代,市场对于人工智能芯片的需求将随着云/边缘计算、智慧型手机和物联网产品一同增长。

未来商用前景不明朗,但应用端需求驱动强烈。以深度学习应用为代表的人工智能应用驱动存算一体技术发展,其能大幅提升性能和降低功耗,有望解决边缘端应用和云端数据中心的功耗和成本问题。

我国人工智能芯片行业周期状态

目前存算一体AI芯片应用场景主要为音频类、健康类及低功耗视觉终端侧应用场景中,落地项目主要是小算力需求场景。在语音识别领域中,存算一体AI芯片不仅能实现语音唤醒功能,并支持通话降噪、声纹识别等功能。此外,健康领域应用也可以通过存算一体芯片实现,由于健康类算法的运算量比语音类更小,芯片功耗相应也更低。

大算力方面,存算一体技术在云端潜在应用场景中有大算力、高能效优势,目前尚未落地,但有巨大发展空间。企业可以从相对蓝海的边缘端推理切入,早期避开英伟达最深的训练软件生态壁垒,在无人车、泛机器人、智能驾驶领域寻找潜在市场空间。

存算一体芯片适用于人工智能场景,如可穿戴设备、移动终端、智能驾驶、数据中心等。按算力大小划分,针对边缘端可穿戴等小设备,其对算力的要求远低于智能驾驶和云端设备,但对成本、功耗、时延、开发难度很敏感。而针对智能驾驶、数据中心等大算力应用场景,在通用性、可靠性、算力方面有极高要求。按边缘端与云端划分,边缘端品牌众多,应用场景碎片化,面临成本与功效的难题。存算一体芯片在边缘端具有高算力、低功耗、高性价比的优势。而云端市场玩家高度集中,英伟达一家独大,算法多样且迭代速度快,芯片售价较高。存算一体芯片以其高能效大算力优势有望另辟蹊径抢占云端市场。

存算一体芯片产业化尚处于起步阶段,目前仍面临产业链上游支撑不足,下游应用不匹配等诸多困局。

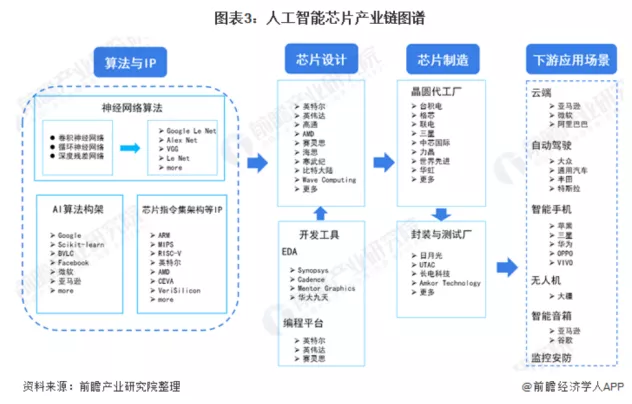

• 上游:算法和IP供应商。

• 中游:芯片设计和芯片制造。开发工具方面,由于大部分存算一体芯片,如基于FLASH的模拟芯片,区别于常规的芯片设计方案,目前市面上无成熟的专用EDA工具辅助设计和仿真验证。

• 下游:应用场景主要聚集在云端、自动驾驶、智能手机、无人机、智能安防等领域。

产业链整合模式分为IDM模式和Fabless-Foundry模式。IDM模式为垂直继承模式,涵盖设计、制造、封装等全流程。Fabless-Foundry模式指垂直分工模式,Fabless企业只负责芯片设计工作,Foundry企业统一对IDM和Fabless等委外订单进行流片。芯片商业模式分类为芯片设计、IP设计授权和芯片设计服务。

1、人工智能发展不及预期风险

存算一体技术应用场景主要为以深度神经网络为代表的人工智能应用,如可穿戴设备、智能家居、智能驾驶等。目前应用端需求为存算一体发展的主要驱动力,但未来商用场景尚未明晰。若人工智能发展不及预期,存算一体公司将面临技术落地困难、产品踏空、收益不及预期的风险。

2、技术路线风险

基于新型存储介质的存算一体技术,需要跨层协同来实现性能(精度、功耗、时延等)与成本的最优。新型存储器较传统存储器有更优越的性能,但同时也面临制造工艺、材料、可靠性、可变性、良率、新型结构与架构的挑战。此外,未来哪一种技术路线成为主流还需要时间来探索与验证。新型存储器介质的发展也可能会有出现更适合存算一体技术的存储器介质。

3、新产品研发风险

随着人工智能应用场景的扩展,未来存算一体芯片的应用场景有望扩增。目前,存算一体芯片尚无成熟的EDA工具辅助验证,导致研发周期较长,且研发成果的产业化具有不确定性。若产品研发进度未达预期或无法在市场竞争中占据优势,公司将面临新产品研发失败的风险,前期的研发投入也将无法收回。

4、产业生态风险

存算一体芯片产业化尚处于起步阶段,目前仍面临产业链上游支撑不足,下游应用不匹配等诸多困局。大规模普及存算一体技术离不开产业生态的建设,需要得到芯片厂商、软件工具厂商、应用集成厂商等的大力协同、研发、推广与应用,实现性能与场景结合与落地。尤其在面对传统芯片已经占据目前大部分已有应用场景的前提下,如何突破新市场、吸引新用户是快速产业化落地的关键。

5、商用落地风险

目前存算一体技术应用场景主要为嵌入式设备、安防监控、智能家居等小算力需求场景,而智能驾驶、无人车等大算力需求场景的存算一体芯片正在研发中。存内计算仅适合原本就对存储需求较大的场景,而对于本身存储需求并不高的场景,为了引入内存计算而加上一块大内存反倒会增加成本适得其反。目前,在人工智能本身仍在探寻应用场景的前提下,存算一体化的落地问题,仍需要紧密结合具体应用场景具体分析。

6、市场竞争风险

目前存算一体市场处于早期百家争鸣态势,多家国内外初创企业陆续开展相关研发。IBM等数十家大大小小企业在投入和探索,广泛分布在存储、计算等领域里,几大技术方向也都在发展中。由于可探索方向很多,技术路径各不相同,且商用方向不明晰,存算一体企业将面临激烈的市场竞争。如何在与其他存算一体公司竞争的同时,从传统芯片行业中抢夺人工智能芯片市场份额,将会是公司需要考虑的关键问题。

存算一体已经被知名研究机构和产业方(达摩院,IBM)确定为下一代技术趋势之一。目前国内外存算一体的公司很多,但都是刚刚起步阶段,差距并不大。存算一体芯片在设计层面是创新的,没有成熟的方法借用。存算一体是模拟系统和存储系统的设计,比标准模拟IP和存储器IP更庞大更复杂,依赖于多次流片而积累的经验,走向成熟预计需要5-10年 。

目前行业主要两类路径,一类是从小算力1TOPS开始往上走,解决的是音频类、健康类及低功耗视觉终端侧应用场景,AI落地的芯片性能以及功耗问题;另一类主要是针对大算力场景>100TOPS,解决大算力问题,与英伟达、华为直面竞争,目前尚未落地,在无人车、泛机器人、智能驾驶,云端领域寻找潜在市场空间。

选择小算力芯片,一般用FLASH/SRAM做存储介质。无论是在音频还是视觉领域对传统架构的AI芯片都具有压倒性的优势。(这个已经得到市场初步验证,苹果下一代AI耳机机的发布会引领国内一大批跟随者)。我们分析如果产品能迅速被市场接受,则可以加速产品的升级迭代,未来就会有更多方案商来一起做产品,会持续产生现金流。等到下一代存储介质RRAM出来,之前的技术积累,无论是模拟计算还是数字计算都可以切换。

选择大算力芯片,一般用SRAM做存储介质,这个介质的存算只能做数字计算,而数字计算的电路功耗都比模拟要大,做不了穿戴,只能去做大算力芯片,对应的应用场景就是智能驾驶和云端服务器。100TOPS以上,比如智能驾驶,基本都是英伟达,华为和地平线在竞争,英伟达是绝对的龙头。但目前自动驾驶场景,无论是传感器,视觉,激光雷达或是毫米波雷达都没有同时使用,也就是说还没有完全融合,所需要的算力暂时到不了100TOPS以上。华为升腾,地平线征程5大概都是100左右TOPS的算力,目前并没有明确场景支撑。未来时机成熟了,还要面对英伟达,华为,地平线的直接竞争,所以个人认为在SRAM这个阶段胜算并不高。针对下一代存储介质RRAM的存算一体芯片,更依赖于RRAM介质本身的发展,即上游FAB的资源导入。无论是做小算力还是大算力目前国内这块整体还属于非常早期的阶段,都有机会,我们计划长期关注RRAM产业链在国内的发展,筛选价值标的。

从投资角度来说:投硬科技早期,主要是投趋势和市场空间。趋势大多数人都能看到,但是里面的技术路径就不是那么好判断了。像通信产业里面的4G(LTE和WIMAX)就是一个很好的例子。再比如存储领域美光的3D xpoint。不是说技术不行,而是技术方向有问题(因为成本太高,产业链生态不成熟)无法量产或是良率上不去。当然如果这个市场足够大,那就更好了。

本次调研得到了多家圈内朋友的大力支持,包括之前华为2012实验室做过达芬奇架构的专家,也包括国内知名存算一体的公司CEO,CTO,和下游的Fab厂,以及存算一体的方案公司,非常感谢大家。虽然大家一致认为这条路很难,也很长,但是只要我们在路上,就已经是很好的开始了。